9 月 14 日消息,台积电等半导体大厂正加速推进面板级扇出封装(foplp)技术的研发与布局,这一先进封装方案正迅速成为行业焦点。

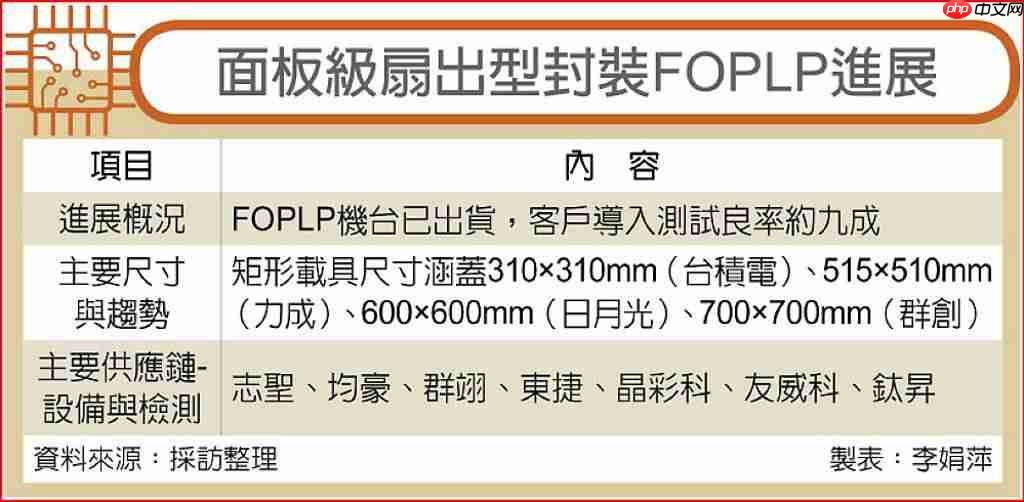

据中国台湾《工商时报》援引供应链消息报道,目前 FOPLP 设备已实现出货,客户导入测试的良率高达九成。然而,大尺寸应用仍处于“验证及小规模试产”阶段,全面量产还需综合评估风险与成本因素。

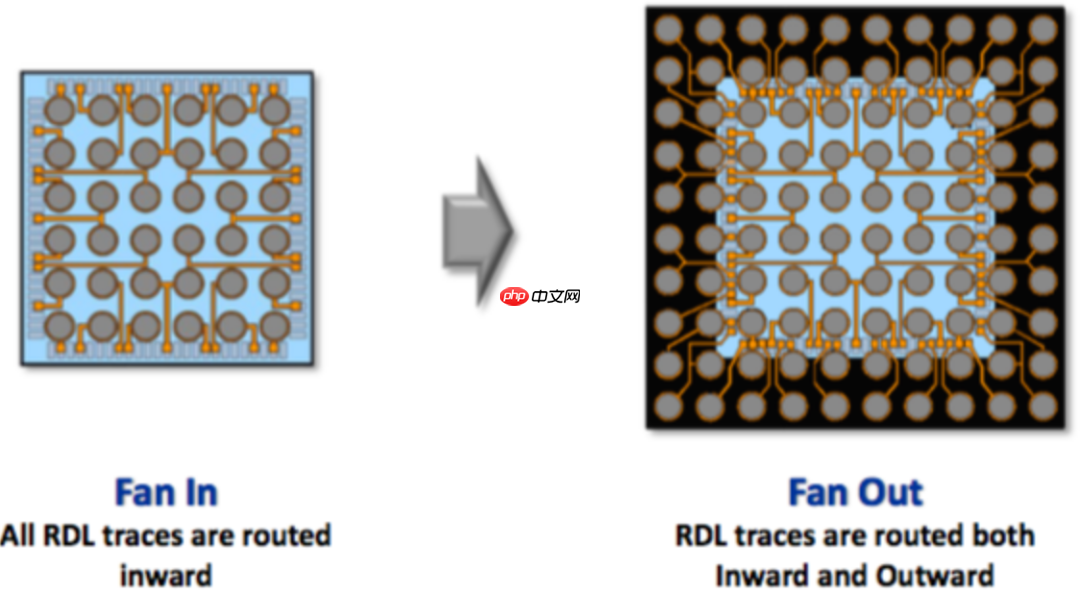

图源:Pixabay注:FOPLP 的全称是 Fan-Out Panel Level Package。在半导体封装中,“扇出”(fan-out)与“扇入”(fan-in)相对。扇入型封装的导线重新分布层(RDL)和引脚均位于芯片投影面积内;而扇出型封装的 RDL 和引脚不仅覆盖芯片区域,还延伸至其外围。

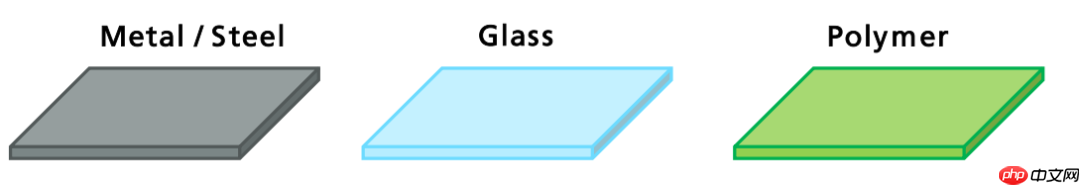

所谓面板级封装(PLP),是相对于晶圆级封装(WLP)而言,即将原本以晶圆为载板的封装方式,改为采用更大面积的面板作为载板。这些面板可由金属、玻璃或高分子聚合物等材料制成。

《工商时报》指出,FOPLP 的核心优势在于使用方形面板替代传统圆形晶圆。相较于扇出型晶圆级封装(FOWLP),FOPLP 采用矩形载板,其中 600×600 毫米的面板面积超过 12 英寸晶圆五倍以上,封装利用率可从约 57% 提升至 87%,显著降低单位成本并增强生产弹性。

报道称,当前业界正采取“双轨并行”的发展策略。一方面,FOPLP 已迈入小批量量产阶段,群创光电与力成科技已率先将其应用于电源管理芯片(PMIC)及电源元件等小型芯片的封装。

另一方面,台积电则专注于开发自有的 CoPoS(Chip-on-Panel on Substrate)方案,旨在为英伟达、AMD 等客户的高性能 GPU 应用提供支持,但其试产过程仍面临技术瓶颈。

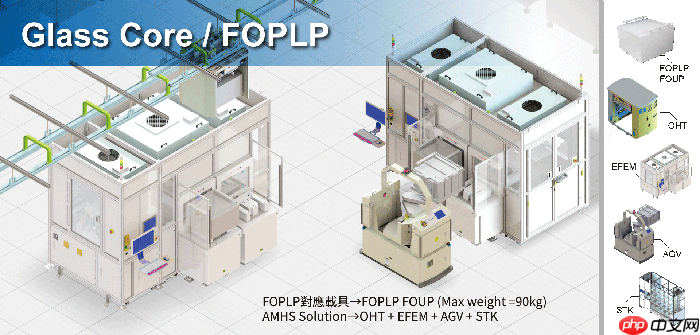

目前,FOPLP 所用载板主要以金属或玻璃材质为主,主流面板尺寸包括:台积电采用的 310×310 毫米、力成使用的 515×510 毫米、日月光的 600×600 毫米,以及群创光电的 700×700 毫米。据悉,力成在引入新一代激光与点胶设备后,试产良率已达 90%,预计明年有望提升至 95% 以上。

在技术研发层面,《工商时报》透露,台积电已组建专门的 FOPLP 研发团队,并规划建立专用产线,同时投入资源发展 PLP(面板级封装)及 TGV(穿玻璃通孔)技术,以推动玻璃基板的应用。原定于 2027 年量产的目标,据供应链消息显示,有望提前实现。

此外,台积电已于今年 8 月宣布将在两年内逐步淘汰 6 英寸晶圆产能,并整合 8 英寸产能以优化生产效率。尽管晶圆二厂(6 英寸)和五厂(8 英寸)是否转型用于先进封装仍在评估中,但业界传闻台积电可能将这些厂区改造为 CoPoS 产线,进一步强化其在先进封装领域的领先地位。